引言

超高速集成電路硬件描述語言(VHDL)是一種用于電路設(shè)計(jì)的高級(jí)語言,與其他硬件描述語言相比,其具有語言簡(jiǎn)潔�����、靈活性強(qiáng)���、不依賴于器件設(shè)計(jì)等特點(diǎn),使其成為EDA技術(shù)通用的硬件描述語言,使EDA技術(shù)更便于設(shè)計(jì)者掌握[1]。

本文依托QuartusⅡ軟件環(huán)境,采用VHDL語言編程,在不修改標(biāo)準(zhǔn)時(shí)鐘電路的基礎(chǔ)上,通過軟件編程設(shè)計(jì)了一款能夠?qū)⒂脩糇飨r(shí)間在標(biāo)準(zhǔn)時(shí)鐘電路中進(jìn)行提醒的作息時(shí)間控制器,該作息時(shí)間控制器實(shí)現(xiàn)了不同作息事件不同提醒程度和方式的設(shè)計(jì)目的����。

1設(shè)計(jì)原理

一款根據(jù)作息時(shí)間的不同,通過不同程度和方式提醒的作息時(shí)間控制器,其提醒和模式設(shè)計(jì)是整個(gè)設(shè)計(jì)的核心。本文充分運(yùn)用VHDL語言"自頂向下"的設(shè)計(jì)優(yōu)點(diǎn),將整個(gè)系統(tǒng)進(jìn)行模塊劃分,設(shè)計(jì)每一個(gè)模塊的功能及各模塊之間的接口,最終確定分為四大模塊:分頻模塊����、時(shí)間調(diào)整模塊、計(jì)數(shù)器模塊以及顯示模塊��。

2功能模塊

2.1分頻模塊

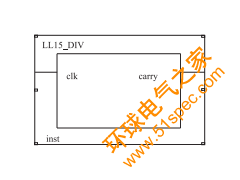

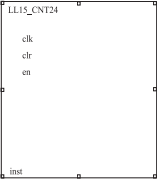

該模塊負(fù)責(zé)輸入時(shí)鐘信號(hào),因?yàn)樵摙騀РA中已有的時(shí)鐘信號(hào)是50>HM的時(shí)鐘信號(hào),所以該分頻器是一個(gè)50M分頻的分頻器,以保證通過這個(gè)分頻器后每一個(gè)輸入信號(hào)是1S,從而使后面的計(jì)時(shí)器每一次計(jì)數(shù)為1S,保證計(jì)數(shù)的準(zhǔn)確��。其Symbol如圖1所示,其中clk為系統(tǒng)時(shí)鐘信號(hào)輸入端,larrz為1HM時(shí)鐘頻率輸出端�。

圖11Hz分頻器symbol

2.2時(shí)間調(diào)整模塊

該模塊負(fù)責(zé)實(shí)現(xiàn)計(jì)時(shí)器的預(yù)設(shè)功能,通過手動(dòng)輸入信號(hào),在計(jì)時(shí)之初就改變計(jì)時(shí)器的初始計(jì)時(shí)狀態(tài)��。計(jì)時(shí)器的最大計(jì)時(shí)時(shí)間是固定的,即23h59min59S,同時(shí)可以手動(dòng)校正與標(biāo)準(zhǔn)時(shí)鐘的誤差���。調(diào)整電路設(shè)計(jì)如圖2所示,該模塊是由一個(gè)非門和一個(gè)二選一或門組成的,其中非門的作用是將輸入的低電壓轉(zhuǎn)化為高電壓,二選一或門的作用是保證標(biāo)準(zhǔn)時(shí)鐘電路正常進(jìn)行的情況下,通過手動(dòng)也能對(duì)時(shí)鐘電路進(jìn)行控制�����。

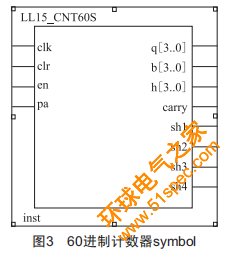

2.3計(jì)數(shù)器模塊

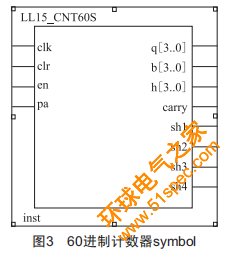

該模塊把分頻器模塊輸出的信號(hào)作為相應(yīng)信號(hào),每有一個(gè)信號(hào)則作用一次,并在這個(gè)計(jì)時(shí)器模塊中加入了暫停和清零兩個(gè)信號(hào)的端口,用另外兩個(gè)可自由控制的開關(guān)給定信號(hào),來控制暫停和清零功能的動(dòng)作與否[4]���。同時(shí)為了完成最大計(jì)時(shí)為23h59min59s,這個(gè)計(jì)數(shù)器模塊由3個(gè)計(jì)數(shù)器組成,2個(gè)60計(jì)數(shù)器用來統(tǒng)計(jì)秒位和分位的時(shí)間變化,1個(gè)24計(jì)數(shù)器用來統(tǒng)計(jì)時(shí)位的時(shí)間變化。其中60秒位計(jì)時(shí)器的輸入端鏈接60分位計(jì)時(shí)器的輸出端,保證每60s顯示1min,60分位計(jì)時(shí)器的輸入端鏈接24時(shí)位計(jì)時(shí)器的輸出端,保證每60min顯示1h,這樣設(shè)計(jì)可以保證計(jì)時(shí)器的計(jì)時(shí)規(guī)律與實(shí)際計(jì)時(shí)規(guī)律相同,更直觀�����。

60進(jìn)制計(jì)數(shù)器其symbo1如圖3所示,引腳c1k是接受從60秒位計(jì)時(shí)器中來的進(jìn)位信號(hào),并把這個(gè)時(shí)鐘信號(hào)導(dǎo)入到模塊中,即實(shí)際中計(jì)時(shí)60s記為1min:引腳c1r是控制清零功能的,當(dāng)系統(tǒng)收到從這個(gè)端口進(jìn)入的信號(hào)時(shí),此計(jì)數(shù)器模塊內(nèi)的所有計(jì)時(shí)結(jié)果清零:引腳en是控制暫停功能的,當(dāng)系統(tǒng)收到從這個(gè)端口進(jìn)入的信號(hào)時(shí),此計(jì)時(shí)器不管c1k口是否有信號(hào),系統(tǒng)均保持計(jì)時(shí)不變,保持當(dāng)前狀態(tài):引腳pa為接受改變亮燈模式的輸入信號(hào):引腳h[3..o]是輸出亮燈模式的類型的信號(hào):引腳q[3..o]是輸出計(jì)時(shí)個(gè)位的結(jié)果信號(hào),能顯示0到9:引腳b[3..0]是輸出計(jì)時(shí)十位的結(jié)果信號(hào),能顯示0到6:引腳carry是輸出進(jìn)位信號(hào),當(dāng)此計(jì)數(shù)器達(dá)到最大值即60時(shí),系統(tǒng)則輸出一個(gè)進(jìn)位信號(hào),同時(shí)系統(tǒng)計(jì)時(shí)結(jié)果清零��。引腳sh1��、sh2���、sh3���、sh4是在達(dá)到作息時(shí)間表中時(shí)間時(shí)向彩燈輸出信號(hào),達(dá)到鬧鐘設(shè)定秒�����、分鐘位效果��。

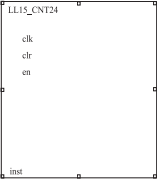

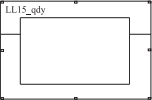

24進(jìn)制計(jì)數(shù)器其symbo1如圖4所示,引腳c1k���、c1r、en與60進(jìn)制計(jì)數(shù)器功能相同��。引腳q[3..o]是輸出計(jì)時(shí)個(gè)位的結(jié)果信號(hào),能顯示0到9:引腳b[3..0]是輸出計(jì)時(shí)十位的結(jié)果信號(hào),能顯示0到9:引腳carry是輸出進(jìn)位信號(hào),當(dāng)此計(jì)數(shù)器達(dá)到最大值即24時(shí),系統(tǒng)則輸出一個(gè)進(jìn)位信號(hào),同時(shí)系統(tǒng)計(jì)時(shí)結(jié)果清零。引腳sh1����、sh2�����、sh3是在達(dá)到作息時(shí)間表時(shí)間時(shí)向彩燈輸出信號(hào),達(dá)到鬧鐘控制時(shí)位的效果�����。

2.4顯示模塊

該模塊用來處理計(jì)數(shù)器模塊的輸出信號(hào),通過相應(yīng)的編碼把計(jì)時(shí)結(jié)果顯示在7位LED數(shù)碼管上,從而使計(jì)時(shí)結(jié)果能夠直觀顯示出來[5]�����。其symbo1如圖5所示,引腳d[3..0]是接受從計(jì)時(shí)器模塊輸出的信號(hào),每一個(gè)顯示模塊與一位計(jì)時(shí)器輸出信號(hào)相對(duì)應(yīng):引腳h[6..0]是把處理后的計(jì)時(shí)器輸出信號(hào)編譯到7位LED數(shù)碼管上,使得每一位數(shù)字能夠顯示出來�����。

圖424進(jìn)制時(shí)計(jì)數(shù)器symbol

圖5顯示模塊symbol

3結(jié)語

本文利用VHDL語言,在Quartus一軟件環(huán)境下進(jìn)行編程設(shè)計(jì)的作息時(shí)間控制器,當(dāng)下載到DE2-115開發(fā)板上進(jìn)行硬件驗(yàn)證,所得結(jié)果滿足設(shè)計(jì)要求��。

在設(shè)計(jì)過程中,發(fā)現(xiàn)作息時(shí)間控制器與我們?nèi)粘K玫聂[鐘等提醒器件相近,但該作息時(shí)間控制器無法與鬧鐘一樣可以讓用戶自己設(shè)定提醒時(shí)間,希望能與讀者共同探討是否能將作息時(shí)間表的設(shè)定交予用戶設(shè)定的合理方案��。